|

Source URL: http://users.ece.gatech.edu/~hamblen/ALTERA/altera.htm (잘못되거나 오래된 Link들은 모두 수정하여 두었습니다...) Source URL: http://users.ece.gatech.edu/~hamblen/ALTERA/altera.htm (잘못되거나 오래된 Link들은 모두 수정하여 두었습니다...)

Video and VHDL Demo Files for Altera's UP 1 and UP 2 Education Boards

Altera's UP 1 Education Board shown to the left, contains a large CPLD,

Complex Programmable Logic Device, that can be used to implement digital

logic designs that contain 20,000 or fewer gates. The UP 1X and the new

UP 2 boards are identical, but they contain a larger 70,000 gate CPLD. A PC-based student version of Altera's CAD tool, MAX PLUS II, provides

support for schematic capture, VHDL based logic synthesis, logic simulation,

and CPLD programming. It is being used in the digital logic and computer

architecture classes at Georgia Tech in the School of Electrical and Computer

Engineering. The design files listed here can be downloaded to this

board via a PC's parallel port cable. The UP 1 board also contains

switches, LEDs, seven segment displays, a VGA connector, and a PS/2 keyboard

or mouse port. VGA Video output can be generated by hardware designs

implemented on the board. Video output directly from the CPLD was

used to generate the images and movies below. Altera's UP 1 Education Board shown to the left, contains a large CPLD,

Complex Programmable Logic Device, that can be used to implement digital

logic designs that contain 20,000 or fewer gates. The UP 1X and the new

UP 2 boards are identical, but they contain a larger 70,000 gate CPLD. A PC-based student version of Altera's CAD tool, MAX PLUS II, provides

support for schematic capture, VHDL based logic synthesis, logic simulation,

and CPLD programming. It is being used in the digital logic and computer

architecture classes at Georgia Tech in the School of Electrical and Computer

Engineering. The design files listed here can be downloaded to this

board via a PC's parallel port cable. The UP 1 board also contains

switches, LEDs, seven segment displays, a VGA connector, and a PS/2 keyboard

or mouse port. VGA Video output can be generated by hardware designs

implemented on the board. Video output directly from the CPLD was

used to generate the images and movies below.

Click

here for more information (PDF)

NEW! We

have a new lab book from Kluwer based on Altera - Click here for more info

NEW! We

have a new lab book from Kluwer based on Altera - Click here for more info

Georgia Tech's UP 1 and UP 2 Board Design Examples

A

note about Altera CAD tool versions

|

LIFE - Implements

Conway's game of life on the VGA monitor. Runs demo with one of two

initial values of life cells.Uses a 64 by 64 pixel graphics display. VHDL

based.

Click

here for rules and additional information on Conway's life game.

Video

Demo Movie (mpeg) |

|

|

|

|

MIPS

- Implements the MIPS RISC processor core with

a VGA monitor display of major busses. Push

buttons single step and reset the processor. Also contains an 8 by

8 character font that might be of use for other

projects needing character display. VHDL based. A

newer version of this model can be found on our book's CD-ROM and is described

in more detail in the last chapter.

Video

Demo Movie (mpeg)

Click

here for instructions on running MIPS demo (PDF)

Click

here for more info on the MIPS VHDL model. |

|

|

|

|

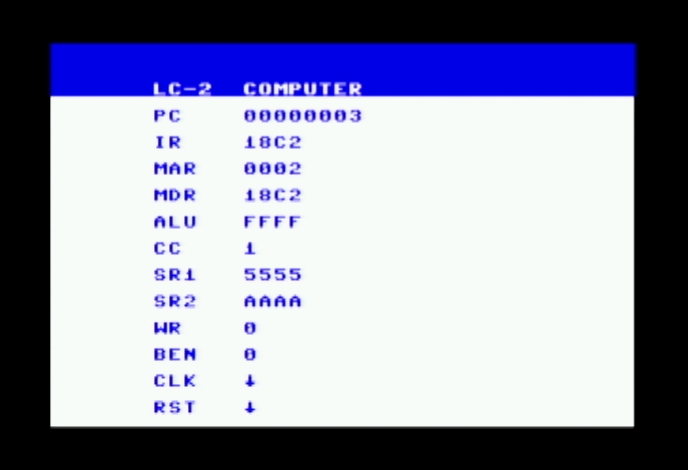

LC2

- is an implementation of the LC2. The LC-2 computer is described in Introduction

to Computing Systems from Bits & Gates to C & Beyond by Yale Patt

and Sanjay Patel, McGraw Hill, 2001. Push buttons single step the processor

and a video output of registers is generated. This web page contains links

to a VHDL model of the LC-2 computer designed to work with the free Altera

student edition and run on a UP 1X board (it is too large to fit on a UP

1 board) |

|

|

|

|

TRAIN

- A virtual model train setup with two trains, three switches, and five

train sensor signals is output on a VGA monitor. Students

write a simple state machine to control the trains and avoid crashes. The student state machine is tcontrol.vhd. VHDL

based. Ideal first VHDL state machine lab assignment, many different

variations on train operation can be given as different assignments. A newer

version of this model can be found on our book's CD-ROM and is described

in more detail in chapter 7.

Video

Demo Movie (mpeg)

Click

here for draft copy (PDF) of Train lab assignment |

|

|

|

|

RAZZLE

- Creates a Fractal type VGA color image with 640 by 480 pixels without

using memory. Very simple design that contains just the basics of

VGA video signal generation.

Video

Demo Movie (mpeg) |

|

|

|

|

DZONE

- Demonstration of our latest D-chip UP 1 graphics technology. Uses both

RLE encoding and color dithering. Programming file (sof) for download

to UP 1 board.

Video

Demo Movie (mpeg) |

|

|

|

|

MOUSE -

NEW!

Demonstration of PS/2 mouse with video output. Plug in mouse and

monitor, power up UP1, and then download this file. Mouse moves cursor

and buttons change cursor color. Additional documentation with source

code can be found in our lab book.

Video

Demo Movie (mpeg) |

|

|

|

|

The

NEW

Low Cost UP1bot is now moving! Construction details and sensor info can

be found in the lab book.

Video

Demo Movie (39M AVI File)

Powerpoint

presentation on UP1bot |

|

|

|

Georgia Tech Student Design Projects

|

Doug, Gauthier, and Mike's Pipelined

DLX and Video Terminal Project Page

Contains a VHDL UP 1 tutorial, and a 5 stage pipelined

DLX RISC processor design. The processor has a video terminal with

drivers for keyboard input and video character generation for output. Vidterm,

programming file (sof) with terminal and keyboard demo.

Video

Demo Movie (mpeg) |

|

|

|

|

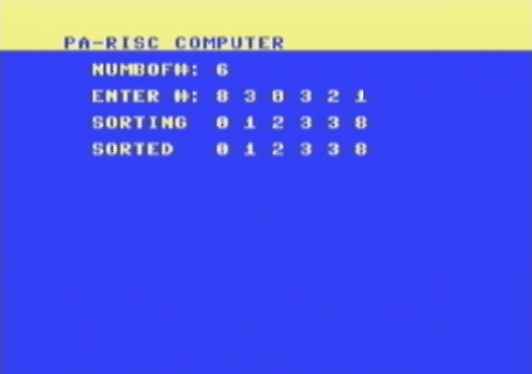

PA-RISC

processor core running an assembly language bubble sort with PS/2 keyboard

input and video output. Runs on a 10K70 - UP1.

Video

Demo Movie (mpeg) |

|

|

|

|

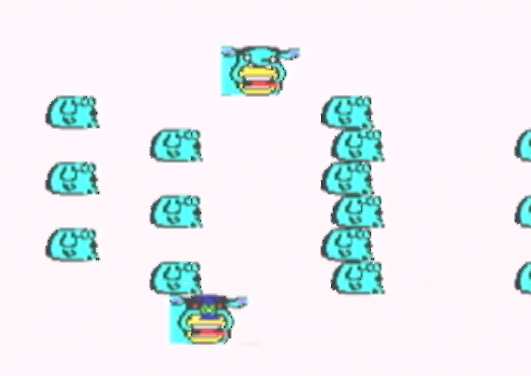

Ticcer

- Clone of the frogger video game with a tic and dogs instead of a frog

and cars. Runs on a 10K70 - UP1.

Video

Demo Movie (mpeg) |

|

|

|

|

Quest8

- Adventure style game with PS/2 keyboard input. Cursor keys move

the character. Find the secret path off of the island. Runs

on a 10K20.

Video

Demo Movie (mpeg)

The

Making of Quest8 (avi) |

|

|

|

|

Megatronixs

Robot Vehicle. This student project uses a UP1 board running our MIPS IP

core. Two Polaroid SONAR units detect walls and try to steer the vehicle. An off-the-shelf RC car base with PWM servo steering and a PWM speed control

was used. Echo return signals from the SONAR generate interrupts.

Movie

(AVI) |

|

|

|

Juergen Vogel's labs for the MAX chip on the

UP 1 Board These introductory digital logic labs use VHDL, the MAX

chip, LEDs, and switches on the UP 1 (no video). This is a draft copy in

MS Word format. Juergen developed these as a special student project at

Georgia Tech.

ALU

- builds a 4-bit 14 function Arithmetic Logic Unit

BUTTON

- debounces the push buttons

LOCK

- a combination lock state machine lab |

|

|

|

Designs from Jean's HDL/UP1-board page

|

PONG

- A VGA pong game. Flex chip pushbuttons move

the paddle.

Video

Demo Movie (mpeg) |

|

|

|

|

WORM

- A VGA version of the classic centipede game. A worm is moving on the

screen, seeking food (green dots) and trying to avoid poisonous stuff (red

dots). Two push buttons are used to navigate the worm, one turns the worm

clockwise, the other counterclockwise. |

|

|

|

Ed Hennesy's UP 1 Slot Machine (Oregon Institute

of Technology)

Bob Reese's Class Web Site (Mississippi State)

EE4743/6743

contains some nice Altera based labs, homework, and tests developed for

EE4743/6743, Digital Systems Design, by Bob Reese at Mississippi

State. Also contains Circles

a Nim variant game for the UP 1 with keyboard input and video output.

Oxford Hardware Compilation Group

|

Boatrace

a video game written in Handel C, a synthesizable C developed at Oxford. |

|

|

|

Documentation for UP 1 and MAX PLUS II Software

Altera 10.1 Student version software

and readme

file.

Student version Authorization

Code

Patch

required for older student version (not used in version 9.23) to program

UP 1 board. If link is down

right

click here and save this driver file in your maxplus directory.

UP

1 Users Guide (PDF) - Information on

UP 1 board jumpers and pin locations

UP

1 Supplement(PDF) - Update to UP 1 Users Guide - corrects some

pin numbers

MAX

PLUS Getting Started (PDF) - Tutorial on Altera

Software

VHDL

Synthesis - A free tutorial on synthesis

of digital hardware using VHDL

VHDL

Help - a windows VHDL help file

MVP

- Georgia Tech's DOS version of Make VHDL Pretty, cleans up messy VHDL

code and makes a text, html, or ps output file. VHDL keywords can be put

in bold and comments in italics in the listing file. HTML output files have colored text

like

the Altera editor. Type mvp without options for command

line syntax. Here is a typical command line mvp -uKF6 -S"My Subject"

-N"Who am I?" my_file.vhd > outputfilename. Use "> printername"

to redirect postscript output directly to a printer instead of a file. Text output can also be produced. Windows beta version of MVP

from Scott Barnes. Latest version of MVP

from Jason Trammell.

A Meta Assembler for Altera Computer Design Projects

- Here is a new link to the meta

assembler. It can easily generate code for the example Altera UP1 based

computer designs in the book (or any others) and it is pretty easy to use. You need to make a definition file that defines instruction formats and

then you have an assembler that outputs object code as Altera MIF files. To make it easier you could give students the definition file for a given

instruction set and they would just use it as a normal assembler. It also

supports macros and produces a typical listing file. The syntax is based

on an old meta assembler from the 70's. I was unable to find any meta assemblers

around on the web. They were pretty popular in the 70's for bit slice when

everyone made up their own instruction set and seemed to have all vanished

in the 90's. Here is a format definition and assembly example for the simple

computer.

Data

Sheet(PDF) for FLEX 10K20 CPLD chip on UP1 Demo Board

Data

Sheet(PDF) for Max 7000 chip on UP1 Demo Board

To view PDF files download the free Adobe

Acrobat Reader

To view MPEG movies download direct show from Microsoft

Purchasing your own UP 2 Board

Altera currently sells only the new 70,000 gate UP 2 board. Contact Info for orders:

Mrs. Ralene Marcoccia

University Program Coordinator

Altera Corporation

101 Innovation Drive

San Jose, CA 95134

Phone: (408) 544-7198

FAX: (408) 544-6666

E-Mail: university@altera.com

Note: Altera's discount offer is limited

to students only.

Here is a suggestion for a power supply, Jameco, DV91A - DC Wall Transformer 9VDC

at 1000MA. Radio Shack also has some but be careful to

get the correct voltage, current,

polarity, and a female 2.5MM x 5.5mm connector. Supplies

over 9V DC and up to 12V DC

can be used but they tend to really heat

up the UP 1's 5V DC on board regulator.

If you plan to use a keyboard or mouse attached

to the UP 1 board a 1000 MA output

is recommended, since the UP 1 must also provide power

to them.

A small heat sink for the UP 1 or 2 voltage regulator

is not a bad idea. DigiKey, HS213

or Jameco, 158051 is small enough to fit in the tight space so that the regulator

can be bent back

down on the board's surface.

A longer 25pin to 25pin PC M/F parallel cable is also

useful since the byteblaster cable

is very short. You will need all 25 wires connected

in the cable. Any computer

store or electronic parts mail order catalog should have

these for a few dollars.

Be sure to get a quality cable with shielding, we have

had trouble with a few of the really cheap cables.

If you ever need to replace the MAX chip, be sure to use

a PLCC extraction tool.

The 84pin AMP PLCC extraction tool available from DigiKey

works well.

This web page is not associated with or sponsored by Altera

Corporation. Altera is a trademark and service mark of Altera Corporation

in the United States and other countries. Altera

products are the intellectual property of Altera Corporation and are protected

by copyright laws and one or more U.S. and foreign patents and patent applications.

Return to UP2 Education Board's Schematic page... Return to UP2 Education Board's Schematic page...

|

![]()