# econe single-chip FPGA news

innovative programmable logic solutions

#### **ESC EDITION**

Visit our Booth #632

# **Afraid of Commitment?**

Processor usage in FPGAs is growing rapidly. For companies without ultrahigh volumes, the primary obstacle has been the contract negotiations and fees typically associated with licensing models for industry-leading processor cores.

Leveraging its partnership with ARM, Actel removes this obstacle, enabling designers to utilize the industry-standard processor of their choice, such as the new ARM Cortex-M1 processor, for use in its

**Cortex on Actel** is Small, Fast, and Free -View Webcast

actel.com/support/Webcasts

Flash-based, single-chip Actel Fusion Programmable System Chip (PSC) and ProASIC3 FPGAs.

Co-developed by ARM and Actel, the 32-bit ARM Cortex-M1 processor is the first ARM processor designed specifically for FPGA implementation.

In eZone read about the details of the Cortex-M1 Processor and how to decide which Actel device would be the best solution for your Cortex design.

Then find out how to design with your Cortex Processor using the Actel Processor Design Flow.

#1 Nonvolatile FPGAs Often imitated... ...never duplicated View Webcast actel.com/support/Webcasts

#### THIS ISSUE

| Cortex-M1 with Actel      | p2 |

|---------------------------|----|

| #1 Nonvolatile FPGAs      | р3 |

| Which Device for Cortex?  | р3 |

| Processor Design Flow     | p4 |

| Build Your Own Processor  | р5 |

| Coverification for ARM7   | р6 |

| Programming over Ethernet | р7 |

| HiRel Processors          | p7 |

| What to see at ESC?       | р8 |

|                           |    |

#### Actel News

Mar 19, 2007 Actel and ARM Develop High-Performance 32-Bit Processor Optimized for FPGAs

Mar 19, 2007 ARM Extends Cortex Family With First Processor Optimized for FPGA

Mar 12, 2007 Aldec and Actel Deliver Co-verification Solution for ARM-based **FPGA** Design

Mar 06, 2007 Actel CEO to Present at 10th Annual Semico Summit

Feb 12, 2007 Actel ProASIC3 FPGAs Selected for Use in Low-Cost Marine Safety and Security Equipment

actel.com/ezone/subscribe

## ONECHIP is all you need

## Your HOT ideas – our COOL solutions

Actel Corporation is the leader in single-chip FPGA solutions

Cortex-M1 with Actel

#### John East » View from the Top

Customers influence and help define what idea is "hot" and what is not.

Therefore, electronics companies are turning more and more toward customer-focused collaboration to facilitate innovation.

At Actel, we've struck a nerve with products optimized to address common technical challenges and issues.

To create flexible, cost-effective platforms, designers are increasingly embedding processors in FPGAs. Most attractive are processors they've used or industry-standard solutions with existing tools and support, such as Actel's free FPGA-optimized ARM Cortex-M1 processor. The availability of an industry-standard option, free of license and royalty fees, enables designers to identify the solution that best fits their "hot" idea.

As system management and the "hot" MicroTCA standard gain importance, highly flexible system management solutions, such as our Fusion mixed-signal FPGAs and Fusion-based MicroTCA reference designs, can reduce system cost and board space while improving reliability.

As "hot" portable, battery-operated applications proliferate, low-power operation is essential. The 5µW Flash-based Actel IGLOO family directly addresses this need.

Do you have a "hot" idea? Come take a look at our cool solutions.

John East CEO, Actel Corporation

# **Cortex-M1 with Actel**

## Is Small, Fast and Free

Actel Delivers the First ARM Processor Designed for FPGAs

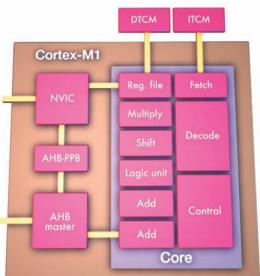

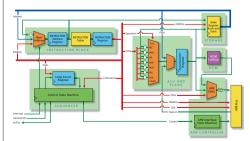

Co-developed by ARM and Actel, the 32-bit ARM Cortex-M1 processor is the first ARM processor designed specifically for FPGA implementation. A streamlined three-stage processor, the Cortex-M1 processor implements a subset of the Thumb®-2 instruction set, retaining compatibility with Thumb code for any ARM processor from the ARM7 processor upwards.

The Cortex-M1 processor, providing a good balance between size and speed, operates at up to 72 MHz in Actel's secure M1-enabled Fusion or ProASIC3 FPGAs. It can be implemented in as few as 4300 tiles, roughly 20 percent of an M1A3P1000.

ProASIC3 device or 30 percent of a mixed-signal M1AFS600 Fusion PSC. The configurable Cortex-M1 processor connects to the industry-standard AHB bus, allowing designers to build a subsystem

### **Cortex-M1 Tools**

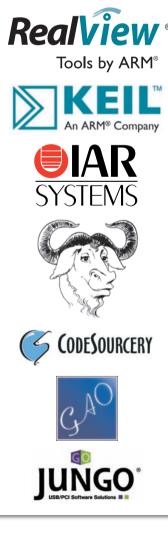

#### Typical of industry-standard offerings, support for the Cortex-M1 processor surpasses that offered for proprietary solutions.

Actel will offer its CoreConsole IP Deployment Platform, SoftConsole program development environment, and Actel Libero IDE – all available for free download from Actel's website. In addition to ARM tools, such as the RealView® Development Suite and RealView Microcontroller Development Kit, third-party vendors like Aldec, CriticalBlue, CodeSourcery, IAR, ImpulseC and Keil will offer supporting tools – from compilers and debuggers to RTOS solutions.

Since the AMBA bus is an industry standard you can use any of the Actel supplied AMBA peripherals, create your own, or use other third party peripherals to complement your processor.

and easily add peripheral functionality. Actel's implementation of the Cortex-M1 processor is now available as early access. The M1-enabled Fusion and ProASIC3 devices will sample in Q3 2007. Pricing for the M1 devices starts at \$3.95.

| SMALL | Roughly 20% of a ProASIC3<br>1 Million Gate device |

|-------|----------------------------------------------------|

| FAST  | 72 MHz in ProASIC3 or Fusion                       |

| FREE  | No license fees or royalties with Actel devices    |

### **Cortex-M1 Dev. Kits**

Since the Cortex-M1 can be programmed into either the ProASIC3 or the Fusion device, designers will be able to use variants of the CoreMP7 and System Management Development Kits to develop with Cortex-M1.

Nonvolatile FPGAs

Devices for Cortex-M1

3

## Leading Nonvolatile FPGAs Actel is the #1 Nonvolatile FPGA Supplier

#### Actel's ProASIC3, Fusion, and IGLOO devices are all based on Actel's third generation Flash architecture. So what do they have in common?

ONECHIP

is all you need

They all share certain characteristics inherent to a true Flash-based FPGA that you won't find on SRAM or Nonvolatile SRAM FPGAs.

Actel devices are truly single-chip, no boot prom, no two silicon, single package combos; one chip is all you need with a true Flash architecture.

Since the devices remain programmed when you power down, they are completely live at power up, with no internal

configuration required while the rest of the system waits. Flash technology is also inherently lower power than other FPGA technologies. 5  $\mu$ W is simply the best out there.

Actel also offers the highest security of any FPGA with 128 bit AES decryption on-chip and no configuration data stream to hack. And if you are familiar with Firm Errors, Actel devices are immune to those as well.

Actel has been supplying nonvolatile FPGAs since 1988 and Flash FPGAs since 1999. Other FPGA vendors are now attempting to imitate the benefits of our truly nonvolatile Flash-based FPGAs. This serves only to validate what Actel has been producing for years... single-chip Flash-based FPGAs.

Leading Nonvolatile Flash-based FPGA

#### The World's First FPGA with Analog Front-End

The Industry's Lowest Power 5 μW FPGA

## Which Device for Cortex-M1?

So now that you've decided you like the Cortex processor you have to choose which Actel device to use it with.

#### **ProASIC3** is the Leading Nonvolatile Flash-Based FPGA

It is a single-chip Flash FPGA array with Flash memory. It has low power consumption, is live at power-up, and can run from a single voltage source, with no auxiliary or programming voltages required. It is reprogrammable and extremely secure with 128-bit AES

decryption, and has the lowest total system cost of any FPGA, with no external PROM, or external clock management.

- $\bullet$  Cortex-M1 on ProASIC3 million gate device < 20% of FPGA logic

- 7 devices under 1 M system gates

- Memory 1k of user flash memory, 144 kbits SRAM

- On-chip PLL and extensive global clocking resources

- Up to 300 digital I/O

## **Fusion** is the System-on-Chip option with FPGA, memory, analog, and clocking all built in.

It can even power itself down and back up, so is great as a system manager. Fusion is the industry's first FPGA with analog front-end. You can execute in place with Cortex-M1, since Flash is fast enough for data and instruction access.

Fusion has built in technology for voltage, current, and even temperature monitoring with up to 32 channels feeding the 12 bit SAR ADC.

- Cortex-M1 on Fusion 600k gate device < 30% of FPGA logic

- Up to 8 Mbits of user Flash memory, with 10ns access time

- Integrated Analog to Digital Converter with up to 600 ksps

- Analog I/O (30 IP/10 OP channels) upto 252 Digital I/O

- Clocking 2 PLL, 100MHz RC Osc, Xtal Osc, Real-Time Counter

Processor Design Flow

w Industry Standard Support

## Industry-Standard Support

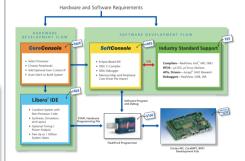

One of the advantages of using industry-standard processors is that it allows designers to use third-party tools that they may already own.

This also eliminates the learning curve of having to learn new tools and architectures before starting on the actual design development.

With industry-standard processors you can get straight to developing the added value that will make your product a success over your competitors.

Here are just some of the industry-standard tools out there that you can use to develop for Actel devices.

For More Processor Info Visit : actel.com/products/mpu/

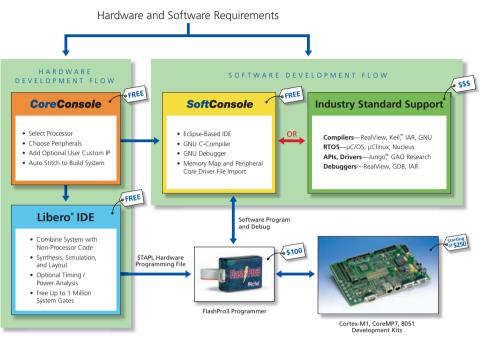

## **Soft Processor Design Flow**

As Actel has become more engaged with processor solutions and partners, we have developed a very simple processor tool suite that will accelerate your design to market.

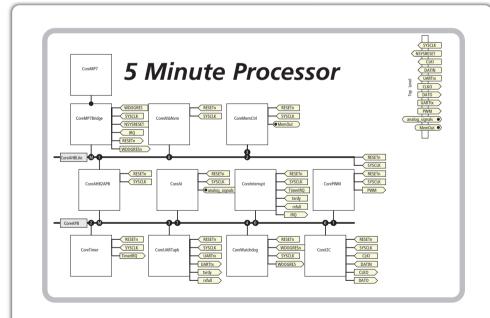

**Building your Processor** CoreConsole is the first step where you build your processor. For example select Cortex-M1 as the engine, then select from a long list of peripherals to build the rest of the processor. If you need UART 10/100, timers, counters etc., they are all available to simply drag onto your screen and auto connect. For a full description read "How to Build your own Processor in Five Minutes or Less" on page 5.

**Programming Your Processor to Silicon** Once you have defined your processor you perform layout using Libero IDE and generate a hardware programming file. Program this to one of our development kits and then all you need is some software code.

**Develop and Debug Application Code** CoreConsole also generates memory map and peripheral core driver files for SoftConsole. SoftConsole is a development environment where you can use GNU compiler and debugger to generate code and debug using FlashPro3. Alternatively use the output of CoreConsole with any number of industry-standard compilers and debuggers.

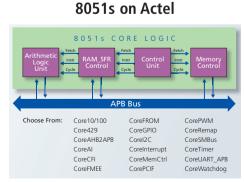

### Choose from ARM7, Cortex-M1, 8051s, and CoreABC

- Compatible with ASM51 instruction set

- One clock per instruction

- AMBA APB bus interface for easy connection of APB peripheral IP cores

- On-chip debug interface

#### **CoreABC Soft Micro**

- Highly configurable and easily tailored to user application

- Use with APB peripheral IP cores

- Can be used in FPGAs that do not have on-chip memory

- Program can be stored in hard gates or in memory

5

#### ONE CHIP is all you need

## How to Build your own Processor in Five Minutes or Less

#### If you are in the habit of using Microcontrollers, then you are probably familiar with the Microcontroller Selector guides.

There are so many to choose from with Atmel, STMicro, and Analog Devices, among others. Armed with your trusty shopping list of things you need in your design, you shop for the right menu combination.

#### Processors Shopping List

Memory = Flash, SRAM how much of each do you need?

Seríal Interfaces = UART, SPI, I2C, MAC 10/100, CAN USB...

Clocking = Timers, counters, 8-bit 16-bit

PWM controllers type and how many channels

RTC and Watchdog of course

ADC, POR, PLL all the usual acronyms

Memory, interfaces, clocks, ADC. That's when you find you only need a 16-bit counter, but that micro only has UART and SPI interfaces, and not I2C or 10/100. Okay, I can add another couple of chips to the system, but board space sure is tight. Well, at least I don't have to worry about I/O. That reminds me, what packages are available for this micro? 144 pin maximum? That's not enough! Ugh, there must be a better way...

#### What if you had a soft processor?

The same one you were planning to use (say an ARM7 or a Cortex) and a menu of peripherals that you could mix and match to build your ideal processor. You have a reprogrammable device to program it to and begin developing code with the ability to create a custom prototype the following day. Not to mention, when marketing changes everything half-way through the design, you can just reprogram and keep going.

## An interesting idea but how long would it take?

- 1. Select your processor ARM7, 8051 or maybe ARM's new Cortex-M1

- 2. Drag and Drop the appropriate buses and bridging (AHB and APB)

- 3. Select and configure your memory interfaces

- 4. Drag and Drop peripherals to the bus

- 5. Auto Stitch and Auto Layout to view your system

- 6. Configure your peripherals and output top level signals

- 7. Generate processor and subsystem

## Hard to Believe?

#### View the On-Demand Webcast

#### **OR** View the Full Processor Design Flow Webcast for the Complete story

## CoreConsole Database Updates

Since CoreConsole is the delivery mechanism for Actel's IP cores, users can update the supported cores via Actel's website.

## The following updates were released in March 2007.

| Core429 v3.0     | CoreAPB3 v2.0     |

|------------------|-------------------|

| Core429_APB v3.0 | Corel2C v3.0      |

| Core8051s v2.0   | CorePCIF v3.0     |

| Core10100 v3.1   | CorePCIF_AHB v3.1 |

| Core10100_       | CoreSMBus v3.0    |

| AHBAPB v3.1      | CoreUARTapb v1.2  |

| CoreABC v2.1     |                   |

For More Processor Info Visit : actel.com/products/software/coreconsole/ CoVerification

#### **Dr Stanley Hyduke**

"CoVer is the only product on the market offering hardware-accelerated HDL simulation environment for hardware designers and high-speed prototyping-like debugging for software developers, bridging the gap between system-on-chip (SoC) engineers. This approach delivers fully synchronized debugging functionality of peripherals, ARM processors embedded in Actel devices and memories from tools like Active-HDL mixed-language simulator and a commonly used GDB debugger."

#### **Dr. Stanley Hyduke** president of Aldec, Inc.

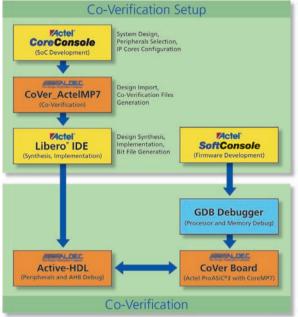

## **CoVer for** CoreMP7

The CoVer solution provides engineers with a complete HW/SW co-verification toolset:

Aldec Active-HDL (Designer Edition) mixedlanguage simulator

Actel's CoreConsole IP Deployment Platform

Actel Libero® Integrated Design Environment (IDE) - Gold edition

Reusable FPGA-based prototyping board with Actel's ARM7-enabled ProASIC3 FPGA and CoreMP7 soft ARM7 core

Software development system, including Actel's SoftConsole program development environment

#### Available now for \$4,995

## **Processor Co-Verification Solution for ARM7**

Worry that a soft processor will give you different results than an off-the-shelf processor? Even though you have to build a support system around the offthe-shelf version to get all the peripherals you need? Putting the processor and all supporting logic in a single chip is more efficient, the question is how do you prove it works on the board?

CoVer<sup>™</sup> is a Windows<sup>®</sup>-based hardware/software co-verification solution. offered by Aldec. It is targeted for Actel's CoreMP7, soft IP ARM7 core, allowing debug of both hardware and software aspects of designs targeted for CoreMP7 in Actel devices. CoVer provides control and visibility across engineering teams, which translates into shorter design schedules and lower project costs.

Utilizing Aldec's patented Smart Clock technology to enable fastest hardware verification and on-demand debugging, the CoVer technology is based on using two clock sources: an HDL simulator generated clock (sw clk) and a hardware oscillator generated clock (hw clk). The programmable Smart Clock unit constantly monitors the AHB Bus to identify bus transactions to Custom Peripherals simulated in HDL. Whenever the transaction to the programmed address range is detected, the system clock is switched to the HDL simulator, allowing for debugging of the AHB bus and peripherals. Once the transaction is completed, the clock is switched back

to the hardware oscillator enabling processor debugging with a speed of prototyping solutions.

The CoVer solution integrates the Active-HDL simulator with the board. The CoreMP7 processor memory and standard peripherals reside in Actel's ARM-enabled M7A3P1000 ProASIC3 FPGA on the board. Aldec's patented sw/hw interfacing allows for the simulation and debugging in Active-HDL waveform viewer. The board is connected to the workstation through 32/64 bit to 33/66MHz PCI slot, providing ease-of-use and high performance. Reprogrammable through PCI or JTAG, the reusable CoVer board can be used for any CoreMP7-based embedded design.

The Active-HDL suite is a comprehensive and totally integrated environment for digital IC design and verification that employs hardware description languages and C/C++ solutions.

It provides engineers and design teams with tools for efficient and vendor independent design implementation and testing. Of course we prefer that you use Actel.

Active-HDL is tailored to support designers working with FPGA families from different vendors. As a part of the suite, pre-compiled Verilog and VDHL libraries of all FPGA silicon vendors are delivered in a readyto-use form.

Active-HDL supports even the most complex FPGA and ASIC designs by providing the following key features:

- Design Entry

- Compiler

- High Performance Simulator

- Debugging

- Co-simulation

- Automated Testbench Generation

- Design Data

- FPGA Vendor Support

- Management

- Coverage and Profiler Metrics

- Documentation

- Legacy Design Support

- Actel Solutions

For More CoVer Information Visit : actel.com/products/solutions/coverification/

FRROE

READY/

ACTIVITY

**Remote Programming Over Ethernet**

**Byte-Tools**

Catapult-EJ1

CATAPULT

FC

# **Remote Programming**

## and Debug Over Ethernet

ONECHIP

is all you need

#### Your design is three days from deadline and you need help from your FAE to debug the last glitch in the system. He's on a training course in California, while you're biting your nails in Minnesota, waiting for him to come back. What if you could plug your board into Ethernet and have the expert debug it remotely for you?

In the world of telecommuting and increased demands on business travel, wouldn't it be easier to be able to work remotely on a system or board and achieve the desired results, without having to fly all the way there just to program it and try something out. Think how much faster you could get a product to market without the travel.

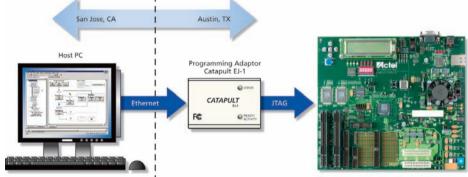

For production systems at customer sites, if you have planned for system upgrades, you can program in the next rev, do a little testing, and never have to visit remote installations. Byte-Tools has developed a remote programming solution for use with Actel's Flash devices. The Catapult-EJ1 programming adaptor allows programming and debugging of a device remotely, through Ethernet, using JTAG protocols.

Each programming / debugging adaptor comes with its unique MAC address, and using Byte-Tool's software, you can assign a unique IP address to communicate through Ethernet. The other end of the adaptor connects through the JTAG header to your board. Use JTAG to send commands to the device through Ethernet, such as erasing, debugging, and programming.

## **Processors for HiRel Applications**

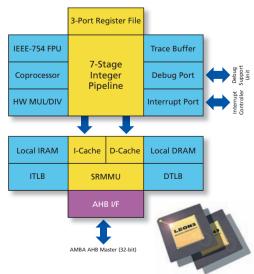

#### The LEON3-FT processor is available as a standard component using the Actel RTAX2000S FPGA.

The fault tolerant design of the processor in combination with the radiation tolerant FPGA gives you total immunity to radiation effects. This makes it ideally suited for space and other highreliability applications.

Leon3 is also available for commercial applications in other Actel devices.

- 32-bit SPARC V8 architecture

- 7-stage pipeline, Harvard architecture

- Optional IEEE-754 floating point unit

- AMBA AHB bus interface

- Instruction and data cache with snooping.

Catapult EJ-1 can be purchased from

Byte-Tools for \$495

Catapult EJ-1 **Configuration Utility** Available free from Byte-Tools

> **STAPL Player** Available free from Actel

STAPL Programming File generated for Actel devices by Libero IDE available free for devices up to 1 Million System Gates

For Remote Programming info visit: actel.com/products/solutions/remprog/

## LEON3 **Development Kit**

The RTAX-S LEON3 development board was developed by Pender Electronics with Gaisler Research to enable the evaluation of the LEON3-FT processor on Actel's RTAX2000S FPGA. LEON3-FT is a synthesizable IP core from Gaisler that implements a 32-bit SPARC V8 embedded processor.

GAISLER RESEARCH

For More Leon3 Info Visit : actel.com/products/solutions/milaero/RTAXSleon3.aspx

## Visit our Booth #632

#### 8 Actel eZone • ESC EDITION

**FSC** Demos

# **HOT ideas** cool solutions... /Acte

### Subscribe for future eZones: www.actel.com/ezone/subscribe

**Register for Product Updates** Stay up-to-date with Actel's latest product documentation: www.actel.com/updates

## Your HOT ideas – our COOL solutions

LLEY

© 2007 Actel Corporation. All rights reserved. Actel, the Actel logo, and Libero are registered trademarks of Actel Corporation. All other brand or product names are the property of their owners. 55900071-0 ESC eZone newsletter